## **Analog Simulation Meets Digital Verification -A Formal Assertion Approach for Mixed-Signal Verification**

| JOHANN WOLFGANG 😨 GOETHE         |  |

|----------------------------------|--|

| UNIVERSITÄT<br>Frankfurt am main |  |

Alexander Jesser, Lars Hedrich

Eberhard Karls

**Department of Computer Science** University of Frankfurt, D-60325 Frankfurt a. M., Germany {jesser,hedrich}@em.cs.uni-frankfurt.de

Stefan Lämmermann, Roland Weiss, Jürgen Ruf, Universität Tübingen **Thomas Kropf, Wolfgang Rosenstiel** Department of Computer Engineering University of Tübingen, D-72076 Tübingen, Germany {laemmerm,weissr,ruf,kropf,rosenstiel}@informatik.uni-tuebingen.de

**Alexander Pacholik**, Wolfgang Fengler **IMFNAU** Computer Architecture Group

Ilmenau Technical University, D-98693 Ilmenau, Germany {alexander.pacholik,wolfgang.fengler}@tu-ilmenau.de

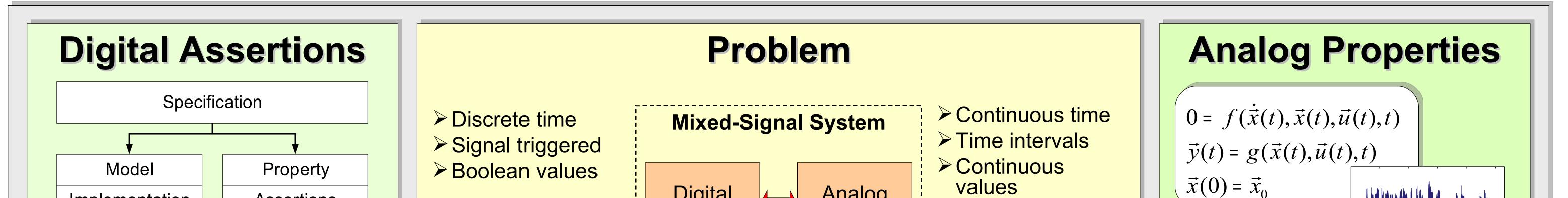

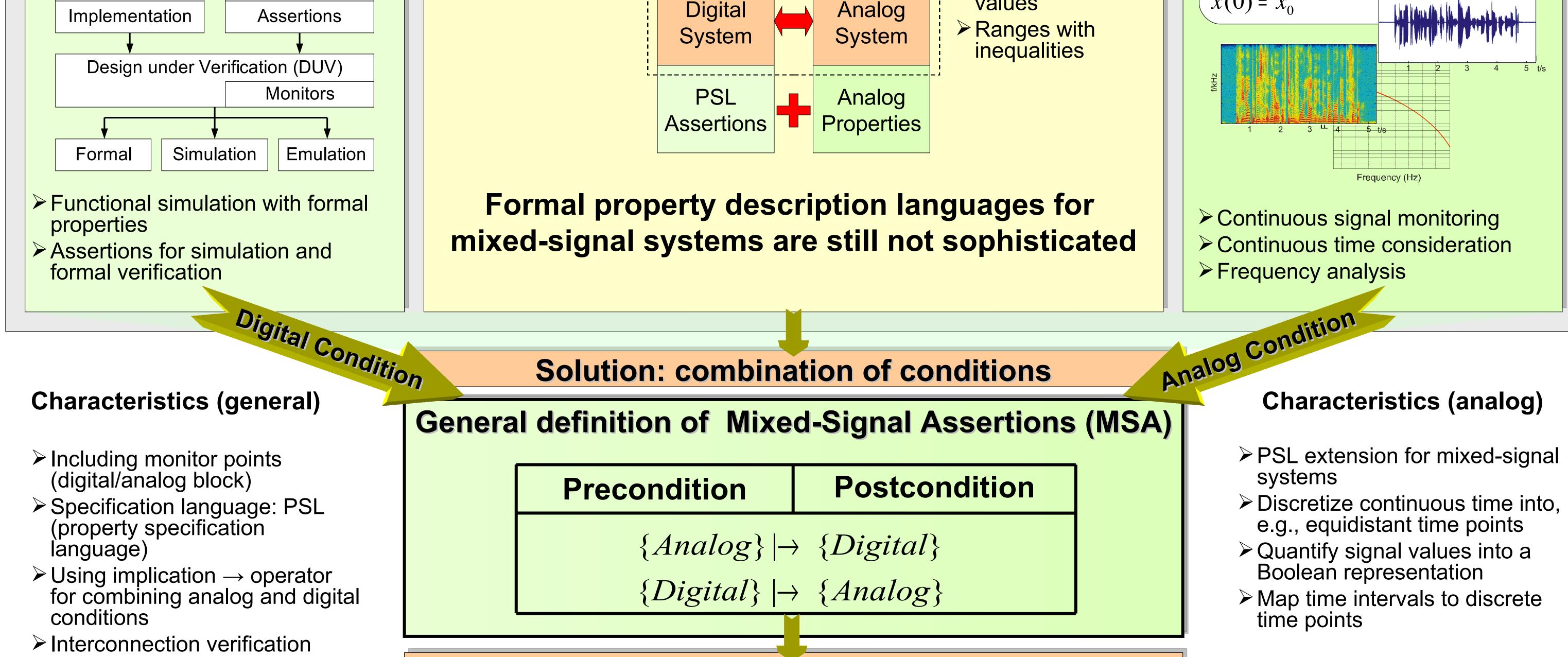

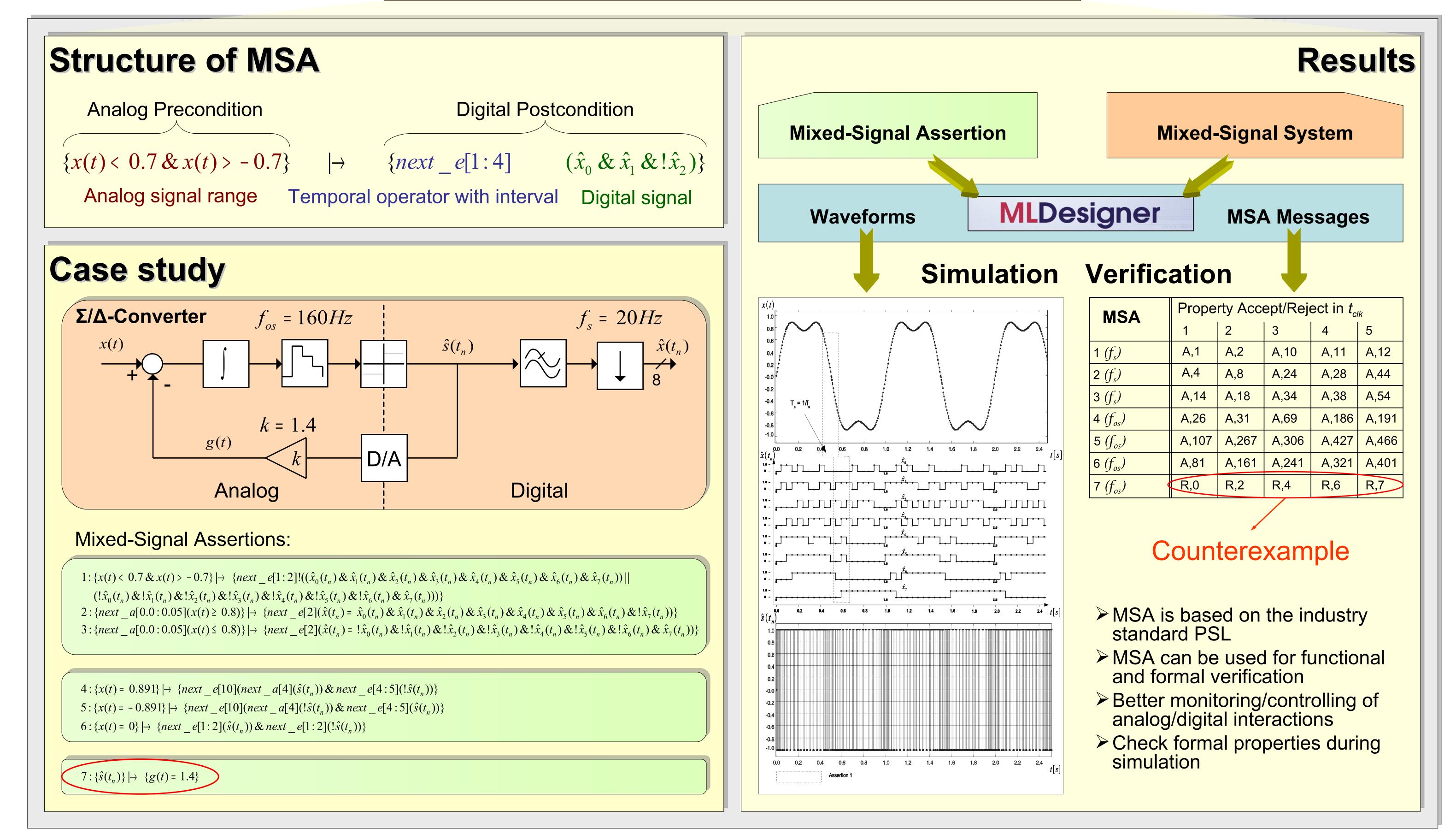

**Abstract**— Functional and formal verification are important methodologies for complex mixed-signal designs. But there exists a verification gap between the analog and digital blocks of a mixed-signal system. Our approach improves the verification process by creating mixed-signal assertions which are described by a combination of digital assertions and analog properties. The proposed method is a new assertion-based verification flow for designing mixed-signal circuits. The effectiveness of the approach is demonstrated on a  $\Sigma/\Delta$ -converter.

## **Simulation / Formal Verification**

14th Workshop on Synthesis And System Integration of Mixed Information technologies SASIMI 2007, Sapporo October 15-16, 2007 This work has been funded by BMBF and edacentrum e.V. within project **F2ST** (No. 01M3072C)